Modelsim is a simulator and is used to simulate HDL languages including Verilog, VHDL etc.

Modelsim is a product of Mentor Graphics and can be easily downloaded with student edition from here: Download Modelsim with Student Licence

This tutorial will explain on how to use Modelsim and how you can use it to program modules in Verilog. See this article “Introduction to Verilog“ if you don’t know Verilog at all.

As explained in “Introduction to Verilog” we will implement “andgate” module in Modelsim

Open Modelsim after installing it.

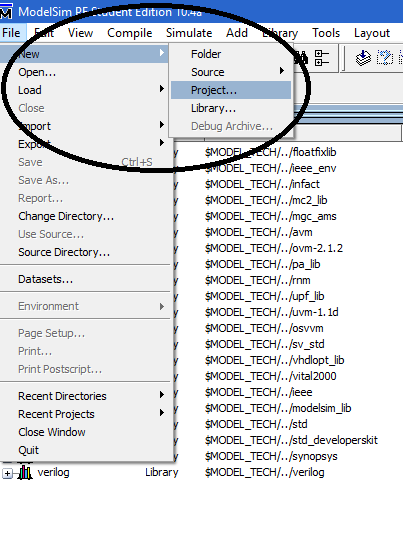

Goto File->New->Project and click Project.

After selecting Project a new window will popup as shown below:

In this window name your project something useful, in this case Project1 was the name chosen. Add the name of the project onto the project location. This keeps the project in an easy to find place

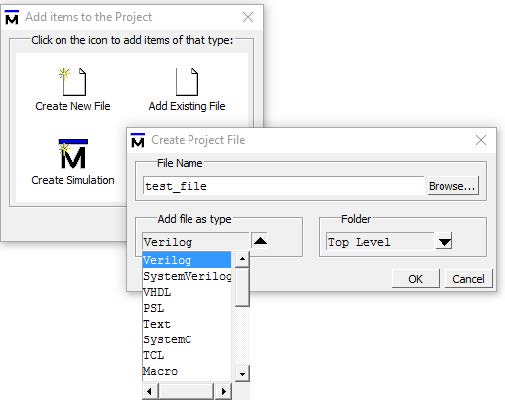

After that you need to create a new file and if this is the first project most likely you will want to create a new file otherwise if you already have created a file then click Add existing file. Click the Create New File button and a window pops up. A project can have more than one files so name this file according to its functionality

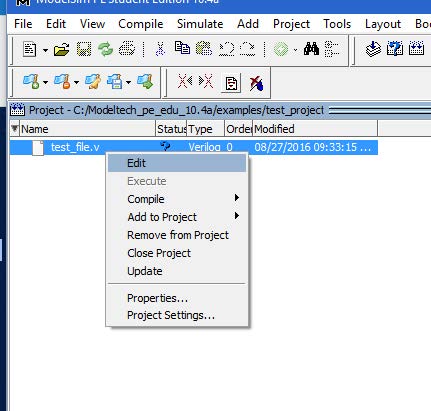

Right click the file name and select “edit”. Now you are going to write Verilog code in this file, Use the following code, This is the same code as explained in “Introduction to Verilog“

module andgate(a,b,out);

input a,b;

output out;

and gate_1(out,a,b);

endmodule

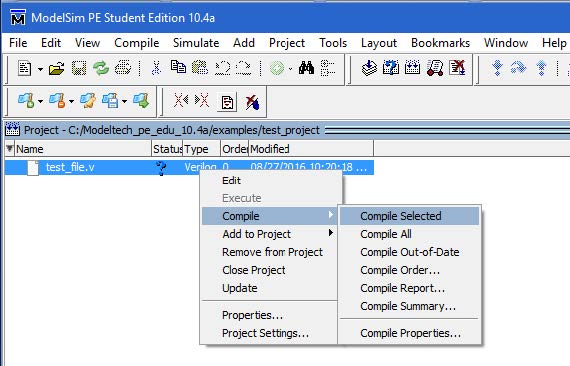

After you complete the code, Right click on file name and select compile.

This step will compile the Verilog file

Now create another Verilog file to write the testbench for you code.

Use the following code for the test bench of AND gate Verilog file.

`timescale 1ns/1ns

module andgate_tb;

wire out;

reg a,b;

andgate mygate(.a(a), .b(b), .out(out));

initial

begin

a = 1'b1;

b = 1'b1;

#5

a = 1'b0;

b = 1'b1;

end

endmodule

Compile the testbench file. Make sure you get no error.

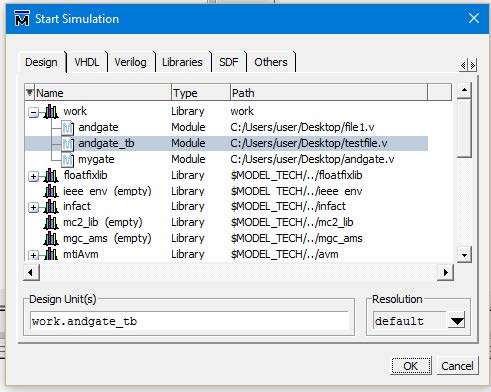

Go to simulate option and select start simulation.

Select test bench file to start the simulation.

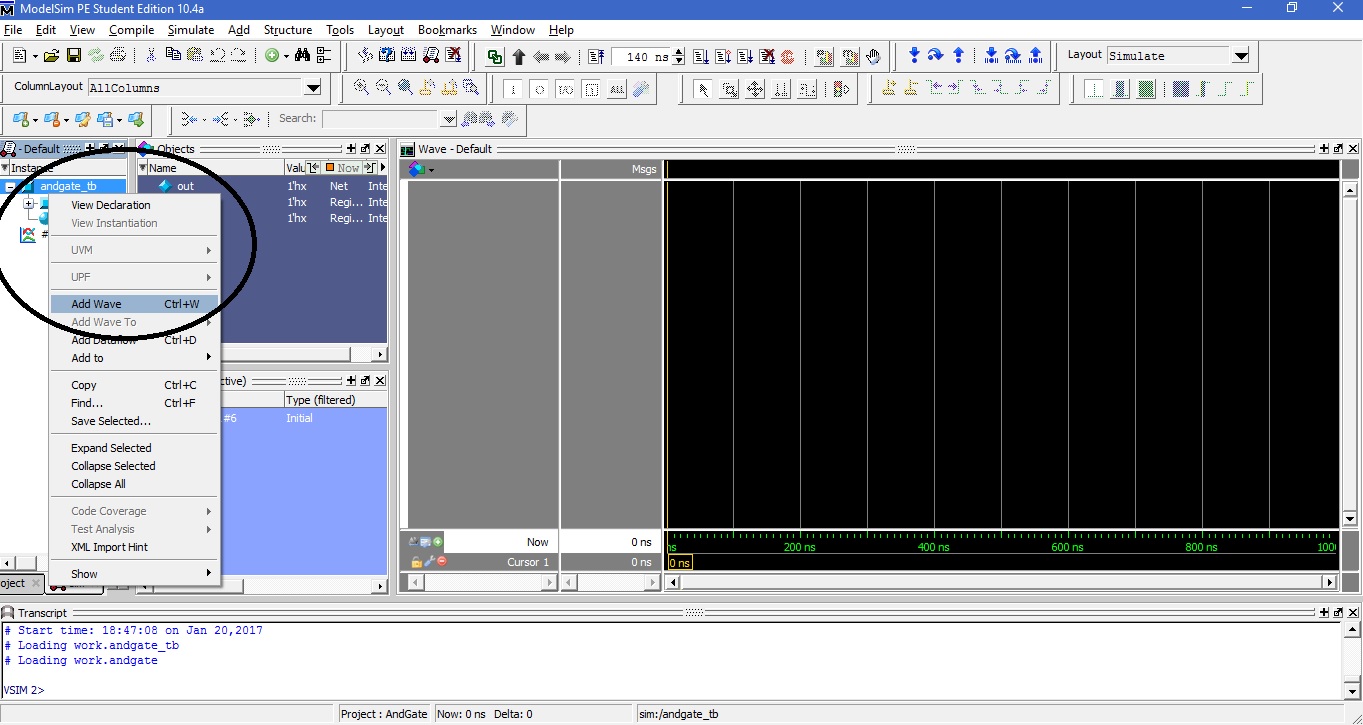

Following window will pop up. Right click on test bench file and select “Add wave”.

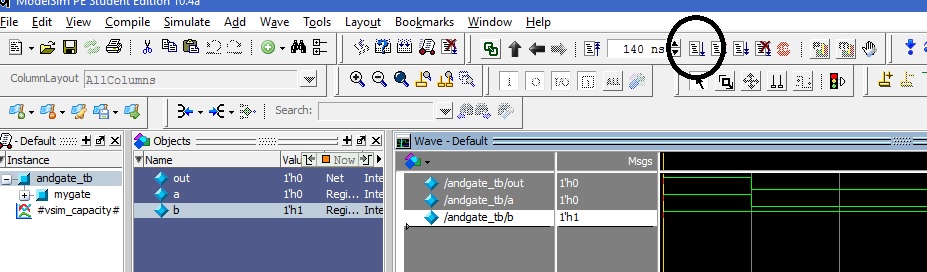

Select “Run”. Make sure you get green coloured waveforms and check your logic as well.

That’s it you have successfully simulated your first Verilog code using Modelsim.